デンソー、米スタートアップとAI半導体開発。クルマの知能化の加速に対応

デンソーと米スタートアップのQuadric(クアドリック)は10月29日、AIの演算処理に特化した半導体のひとつであるNPU(※1)に関する開発ライセンス契約を締結。デンソーはクアドリックのChimera GPNPU(※2)のIPコアライセンスを取得し、両社で車載用半導体IP(NPU)の開発に取り組む。

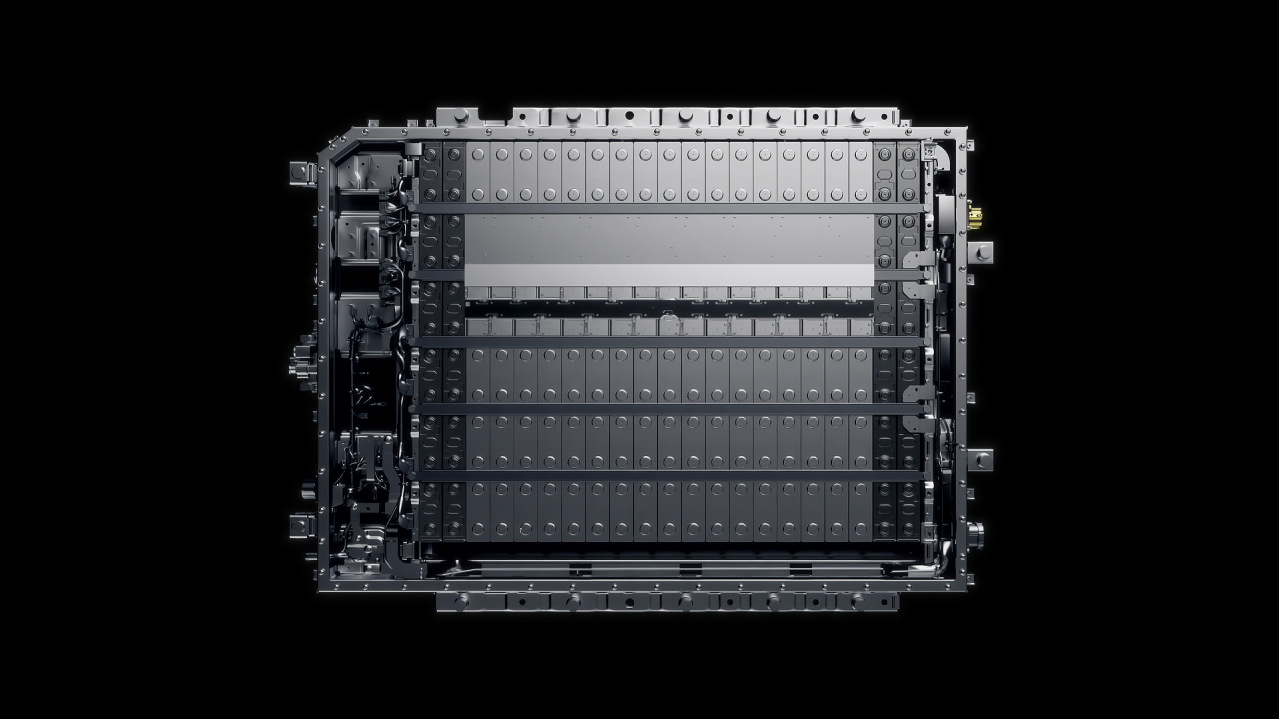

自動運転やコネクティッドなど、クルマの知能化の進展に伴い、クルマは車載センサーから得た膨大な情報のほか、車間・クラウドとの通信から得た情報をリアルタイムで処理する必要がある。そのため、大量の情報を高速に効率よく処理できる車載SoC(※3)の性能がますます重要だとしている。

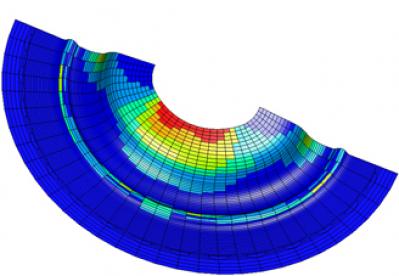

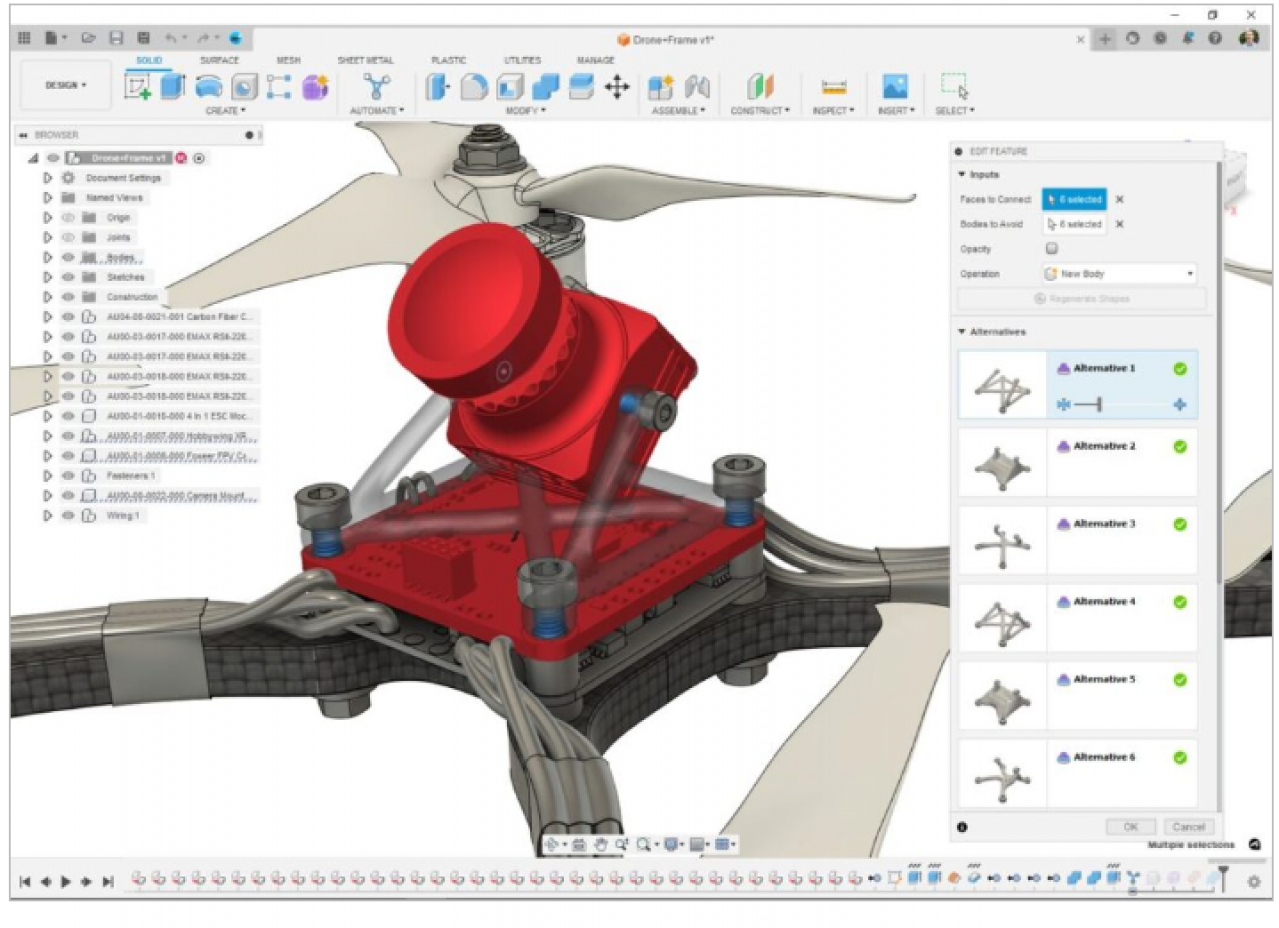

デンソーとクアドリックは、これまでも車載SoC向けにChimera GPNPU(General Purpose Neural Processing Unit)を用いた半導体IPの開発を検討してきたが、今回、デンソーのRISC-V(※4)ベースのプロセッサーとクアドリックのChimera GPNPUを組み合わせた車載用半導体IP(NPU)の共同開発を正式に進めていくことを決定した。

デンソーのRISC-VベースのプロセッサーIPは、ISO26262のASIL(※5) Dに対応しており、安全性の確保が重要となる自動車に最適だという。

クアドリックのChimera GPNPUは、行列演算とベクトル演算、およびスカラー(制御)コードを1つの実行パイプラインで処理できる特有のアーキテクチャー(設計構造)を持つことで、多様な演算処理にフレキシブルに対応できるため、様々なAIに適用できる。Chimera GPNPUを用いることで、車載製品のシステム開発者は将来にわたり独自のAI機能を追加することができる。

両社は、新たな半導体IP(NPU)の共同開発を進めることにより、製品開発からリリース後まで、長期間に渡るAI潮流の変化に柔軟に対応可能な車載SoC実現へ貢献するとともに、より安全性の高いAD/ADAS(※6)製品の開発を推進する。

※1 : NPU(Neural Processing Unit):AIの演算処理に特化したプロセッサー

※2 : Chimera GPNPU(Chimera General Purpose Neural Processing Unit):クアドリックのプロセッサーアーキテクチャの名称

※3 : SoC(System on a Chip):複数の機能を集積し、システムとして機能させる集積回路

※4:RISC-V:オープンな仕様のもと、誰もが自由に扱える命令セットアーキテクチャー(ISA)

※5 : ASIL(Automotive Safety Integrity Level):自動車安全水準

※6 : AD/ADAS(Autonomous Driving/Advanced Driver Assistance System):自動運転/先進運転支援システム